Using CPLD to solve the challenges of portable product design

The proliferation of portable products such as mobile phones, portable media players, handheld game consoles and digital cameras has put system designers under increasing pressure. They must constantly develop and provide products with new features and functions, and try to shorten the time to market. So, what benefits can CPLD bring to portable design? What are the main design factors to consider when choosing a logical solution for portable applications?

Handheld products have been widely used, such as the proliferation of portable products such as mobile phones, portable media players, handheld game consoles, and digital cameras, which has put system designers under increasing pressure. They must constantly develop and provide products with new features and functions, and try to shorten the time to market. According to the prediction of market intelligence company iSuppli, the revenue of core semiconductor products in the above fields is expected to increase from 26 billion US dollars in 2008 to 30 billion US dollars in 2012, which is equivalent to a compound annual growth rate of 4% (core devices are produced by iSuppli Defined, such as ASSP, ASIC and programmable logic devices).

Because of the low standby power consumption, small circuit board size and low cost, the logic functions of portable products used to be provided by application-specific integrated circuits (ASIC) and application-specific standard products (ASSP), and the application of programmable logic devices (PLD) is quite limited. However, with the improvement of programmable device architecture, reduction of power consumption, and the use of new packages to reduce the size and cost, designers began to use PLD more and more, because compared with ASIC and ASSP, PLD in There are inherent advantages in shortening time to market and design flexibility.

CPLDs are used in portable products. Complex programmable logic devices (CPLDs) are generally used for power-on timing, level shifting, timing control, interface switching, I / O expansion, and discrete logic functions. CPLD can be powered on in just a few microseconds, which allows it to control the power-up timing of other devices in the system.

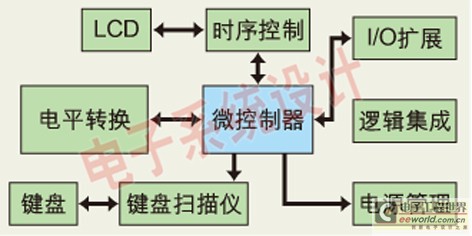

In portable systems, CPLD is also used to connect multiple devices with different operating voltages. For example, in a mobile phone, the microcontroller needs to be connected to peripheral devices, timers, and memories that operate at different voltages. The latest generation of CPLDs can be connected to different voltages between 3.3V and 1.5V because they have a core power supply voltage (Vccint) independent of the output voltage (Vccio). Each I / O group of CPLD can be configured as an independent operating voltage corresponding to the interface of the logic device. Figure 1 shows the CPLD function in a typical portable system.

Figure 1: CPLD function in a typical portable system.

General I / O expansion is another area where CPLD can work with microcontrollers, ASICs, or ASSPs. It increases the total number of available I / Os. An additional advantage of CPLD is that it can interface with peripherals and can be reprogrammed. CPLD can also be used for interface conversion, connecting different interfaces such as I2C, SPI and memory, as well as implementing timing control of liquid crystal panels in portable systems.

When choosing a logic solution for portable applications, designers should consider the main factors include: time to market, design flexibility, standby power consumption, circuit board size, and system integration options.

Product life cycles with shorter time-to-market and design flexibility pose new challenges for handheld device designers, who must provide new products and new features that consumers expect. For high-volume products, ASIC may be able to provide lower unit prices, but ASIC's one-time engineering cost (NRE) is high and development time is very long. If the function of the ASIC is wrong, or the design needs to be redeveloped due to changes in industry standards or market requirements, it will again incur very high costs, including engineering resources, new masks and software design tools. In addition, from starting to implement new modification schemes to tape-out to mass production, this process takes a long time, usually a few months to a year.

Compared with ASIC, ASSP has a lower NRE because many customers are using them. However, they limit the designer's ability to provide product differentiation.

CPLD enables designers to develop, test, and modify designs as they wish, without incurring any mask costs or design fees. Due to the reprogrammable nature of CPLD, even if the equipment has been installed on site, designers can still use software design tools to correct errors and upgrade products at the last minute. Therefore, designers can respond to changing requirements and standards, and quickly provide new differentiated products to the market without having to do any design or redesign the circuit board.

Power consumption CPLD power consumption is usually divided into two parts: static power consumption and dynamic power consumption. Static power consumption refers to the power consumed in the device without signal transitions. Dynamic power consumption is the power consumed in the case of signal jumps in the device, and is proportional to the internal capacitance, jump frequency and jump voltage. For portable systems, standby time is a key design factor, because designers should try to reduce the static power consumption of logic circuits to maximize the time interval between battery charging or replacement. The maximum static power consumption of today's low-power CPLD is 10 ~ 150uA, which mainly depends on the logic density of the device.

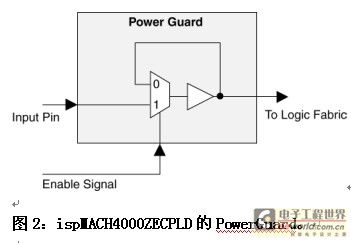

To further reduce power consumption of the entire system, some CPLDs allow users to selectively turn off unused input pins (called “input strobesâ€), including enabling multiplexing between I / O pins and input buffer Applicator, and related circuits in CPLD (as shown in Figure 2). When the enable signal is activated, all inputs are isolated or turned off, so that any input changes will not cause changes to the internal pins. Therefore, even if the input of the I / O pin changes, it will not affect the internal dynamic power consumption of the device.

For example, in Lattice Semiconductor's ispMACH 4000ZE CPLD, all I / O pins in a block share a PowerGuard (for input strobe, LatTIce gives the name of this feature) enable signal, called block input Enable (BIE) signal. BIE can be generated internally using macrocell logic, or it can be generated from external sources or input pins through user I / O. In order to increase the design flexibility, the device has as many blocks as there are input enable signals, ranging from 2 to 16. Two or more enable signals can be combined to form a user enable signal.

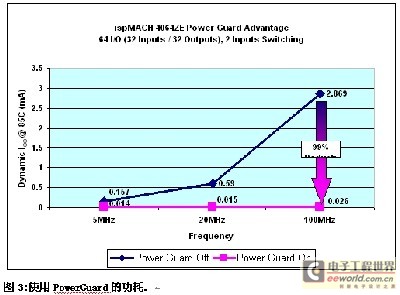

Taking the ispMACH406? ZE device of 6 macrocells as an example, in addition to the two active inputs, the rest use PowerGuard, which reduces the dynamic current by 99%. As shown in Figure 3, the dynamic ICC is reduced from 2.9 mA to 26 μA.

Some CPLDs can individually control each pin through software to make it "high" or "low", thereby further reducing I / O current and total system power. The input hysteresis circuit with a typical voltage of 250mV ~ 500mV is usually used to achieve noise reduction and slow down the change of the input signal to improve signal integrity.

Since the typical value of the main system power supply is 1.8V, most portable systems require an LVCMOS interface. These systems are required to be able to connect with other devices working in TTL or LVCMOS standards. At present, all CPLDs have independent core voltages and I / O voltages, of which I / O voltages can support 1.5, 1.8, 2.5, and 3.3V LVCMOS levels. CPLDs such as ispMACH 4000ZE can also interface with traditional 5V voltage LVCMOS devices.

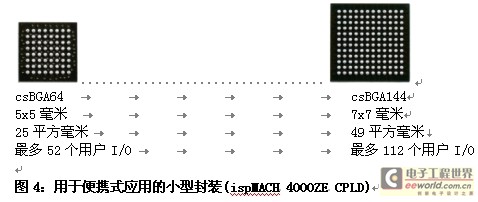

The size of the circuit board is shrinking with the volume of portable products, and designers must integrate more logic functions on very small circuit boards. Now CPLDs can be used in ultra-small packages, including chip-level BGA (csBGA, 0.5 mm pitch), requiring only 25 mm2 or 49 mm2 of circuit board area. The traditional thin quad flat package (TQFP package, 0.8 mm pitch) package requires a circuit board area of ​​100 mm2 or 196 mm2.

When board space is limited, these packages are ideal. Compared with traditional TQFP packages, these packages reduce the circuit board area by more than 75%, which simplifies circuit board wiring and reduces the overall system cost. Figure 4 is a schematic diagram of the ispMACH 4000ZE csBGA package. BGA packages have a lower thermal resistance value (typically 10 degrees / watt) than TQFP or PQFP packages (typical values ​​are 20 degrees / watt to 40 degrees / watt). They are better for reducing power consumption and improving device reliability s Choice.

System integration can reduce the total system cost by reducing the components on the circuit board. When multiple circuit board components are used, manufacturing costs, including assembly, packaging, and shipping, increase the total circuit board cost. In addition, the more components on the circuit board, the higher the failure rate, which is due to the residue between the solder balls and other random failures.

Reducing components can also reduce power consumption. Today, low-power CPLDs are used to integrate external clock sources and standard discrete logic devices, such as the 7400 series logic devices. A single programmable logic device can be used to integrate multiple discrete 74xxx devices, and can also implement other functions, such as I / O expansion, level translation, and timing control.

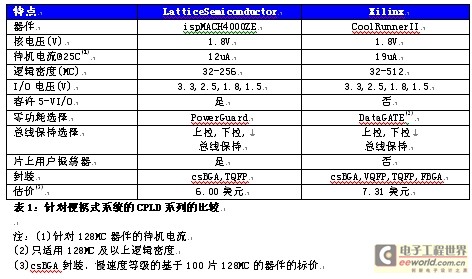

For system integration, in addition to the macrocells with a logic density of 32 to 256 on the device, the ispMACH 4000ZE CPLD also has on-chip user oscillators and timers, keyboard scans, and display controller functions for power-up timing. The typical frequency of the oscillator output is 5MHz, and it can be further divided into 128 (7-bit), 1024 (10-bit) or 1048576 (20-bit) to work at a lower frequency. The benefits of using the integrated oscillator in the CPLD are reduced board cost, simplified inventory management, and minimum risk of product expiration. These factors are often related to the use of discrete components. The table below compares the latest generation CPLD series that can be used in portable systems.

Comparison of CPLD series for portable systems.

In this article, CPLD is being more and more widely used in portable products, with the advantages of zero standby power consumption selection, area-saving ultra-small package and enhanced system integration functions. Compared with the ASIC and ASSP used in the past, CPLD provides designers with a low-cost system solution with significant advantages. In addition, CPLD enables designers to add new features and functions in a shorter period of time according to consumer needs, making products faster to market and less risky.

Female Header Connector,Single Row Female Header Connector,U-Type Female Header Connector,Single Row U Female Header Connector

Dongguan Yangyue Metal Technology Co., Ltd , https://www.yyconnector.com