The BRAM in Spartan-6 stores 18Kbit of data and can be configured as two independent 9Kbit BRAMs or one 18Kbit BRAM. Each RAM can be addressed by two ports or as a single port of RAM. The BRAM contains output registers to increase pipeline performance. BRAM is arranged in columns in the device, the number of which depends on the capacity of the Spartan-6 device.

The functions of BRAM are described below.

Each BRAM has a storage capacity of up to 18Kbit.

A BRAM can be split into two independent 9Kbits or as an 18Kbit.

Each 9Kbit BRAM can be set to a simple dual port mode to double the data width of the BRAM to 36bit. The simple dual port mode is defined as having a read-only port with a separate clock and a write-only port.

Separate synchronous set/reset pins that independently control the set/reset operation of the output registers and latches. Better compatibility with other FPGA families.

18-bit or 36-bit wide ports have different write enable signals, which are commonly used for interface connections to on-chip microprocessors.

Depending on the state of the Write Enable (WE) pin, all outputs have a read or write-side read function. The read-and-write output has three modes of operation: WRITE_FIRST, READ_FIRST, and NO_CHANGE.

A clock is required for the write operation.

A clock is required for the read operation.

All output ports are latched. The state of the output port remains unchanged until the port performs a read or write operation again. The default BRAM output is in latch mode.

The output data path has an optional internal pipeline register. This register mode is strongly recommended to allow the BRAM to operate at a higher clock rate, but with a one clock cycle delay.

Spartan-6's BRAM is similar to other Xilinx FPGA BRAMs. It supports write/read synchronization operations. The two ports are symmetric and completely independent, sharing data, and each port can change its bit width and depth as needed. The memory contents can be cleared or set when the bit stream is configured.

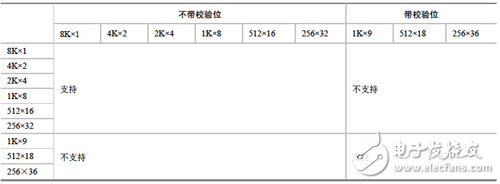

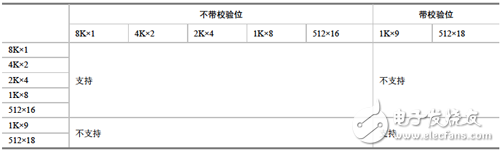

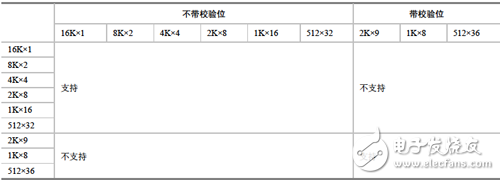

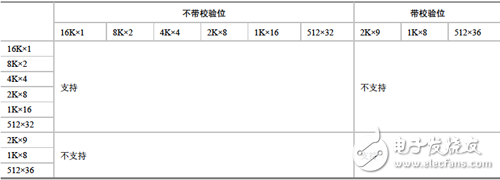

The BRAM configuration in Spartan-6 is very flexible, as shown in Table 2-10 to Table 2-13. When BRAM is configured in full dual-port mode, each port supports write or read operations; when BRAM is configured in simple dual-port mode, port A only supports write operations, and port B only supports read operations.

Table 2-10 Simple dual port configuration of 9Kbit BRAM

Table 2-11 Full dual port configuration of 9Kbit BRAM

Table 2-12 Simple dual port configuration of 18Kbit BRAM

Table 2-13 Full dual port configuration of 18Kbit BRAM

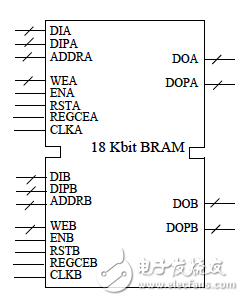

Each BRAM can be configured as a full dual-port RAM with 18Kbit of memory and two completely independent access ports: A and B. The structure is symmetrical. Port A has independent addresses, data input, and data output. Clock, clock enable and write enable signals. Data can be written to one or two ports, or read from one or two ports, as shown in Figure 2-30.

Figure 2-30 Full Dual Port RAM

It should be noted that when two ports operate on the same address at the same time, since there is no special monitoring logic inside the dual port RAM, user monitoring is required to avoid conflicts. The simultaneous operation of two ports on the same address does not damage the physical space. Please refer to the user guide for detailed timing of reading and writing.

Each 9Kbit or 18Kbit BRAM can be configured as a simple dual port RAM. The difference is that port A is a write operation, port B is a read operation, and both reads and writes can occur simultaneously.

The primitives for full dual-port RAM and simple dual-port RAM are shown in Table 2-14 and can be instantiated directly in the HDL code.

75W Medical Power Supply,75W Medical Device Power Supply,75W Medical Power Adapter,75W Rade Power Supplies

Shenzhen Longxc Power Supply Co., Ltd , https://www.longxcpower.com