Plasma display power reduction technology

At the beginning of 2009, there were reports on the EU's ban on plasma TVs in many domestic and foreign media. Paul Gray, head of the European Union Television Industry Research Association, denied this claim, but also mentioned that the association has the following plans.

â— The minimum standard for energy efficiency of flat-panel TVs will be set, and the maximum limit of energy consumption will be set according to the different sizes of the screen.

â— It will be mandatory to require the TV's standby energy consumption to be less than 1W. This requirement will be given to the manufacturer for approximately 1 year.

It can be seen that although the EU does not currently propose a proposal to ban the sale of plasma TVs, there will still be a clear limit on the power consumption of such products, including standby power consumption and average power consumption. This forces us to make unremitting efforts to improve and study how to reduce power consumption, improve power factor, and improve luminous efficiency.

So, in what areas can we optimize and improve to effectively reduce the power consumption of the PDP machine? Below we make a qualitative analysis of this.

1 Power supply part of the power supply as an important part of the PDP requires high efficiency, small size, can provide large transient output power, and has the function of protection function and different output voltages to start in sequence.

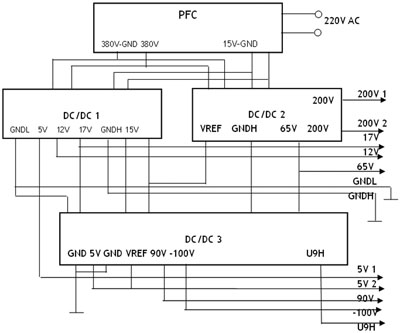

The traditional PDP power supply generally adopts a two-stage scheme, that is, a power factor correction (PFC) level + DC/DC conversion circuit topology. They each have their own switching device and control circuit. Although it can achieve good performance, it is too large, costly, and complicated. Therefore, optimization and transformation of it has become a direction of PDP power supply technology research.

The analysis shows that the PFC module and the scan drive electrode DC/DC converter module occupy a considerable proportion regardless of the angle of transmission energy or the volume occupied. Therefore, the transformation of these two parts has become an entry point for the optimization and transformation of PDP switching power supply.

There are two current optimization options.

â— Single-stage power factor correction circuit (SSPFC)

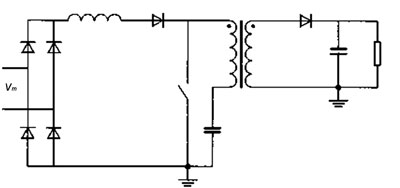

As shown in Figure 1, the SSPFC's small size and simple circuit make it a preferred solution for miniaturization of PDP switching power supplies. The basic principle is: adopting a single-stage power factor correction converter circuit topology, after single-phase alternating current is full-wave rectified, the two inductive ICSs are connected in series to the double-tube flyback DC/DC conversion unit. During half of the power frequency cycle, only a part of the time inductor LB current continuously works. When the input voltage is an AC sine wave, its input current is an approximate sine wave containing high frequency ripple. The phases are basically the same, which increases the power factor at the input.

Figure 1 Single-stage power factor correction circuit

â— Power factor control chip is used as shown in Figure 2. Power factor control chip such as MC34262 can be used for active power factor correction.

Figure 2 Power factor correction circuit using MC34262

The DC voltage of the AC mains after full-wave rectification is divided and input to one input of the multiplier in the control chip, and the error amplifier output voltage is applied to the other input of the multiplier. The multiplier's transmission curve is linear over a large dynamic range. The multiplier output voltage controls the threshold voltage of the current sampling comparator. When the voltage is greater than the threshold voltage, the inductor releases energy. This threshold voltage is approximately proportional to the input voltage, which is approximately proportional to the DC voltage after AC mains is full-wave rectified. When the current in the inductor drops to zero, the inductor begins to store energy. The average current exhibits a sine wave in phase with the mains voltage, making the power factor close to "1".

2 The driving circuit part of the total power consumption of the PDP is not only the gas discharge power consumption, because in the driving circuit of the PDP, a high-power, high-frequency switching circuit is required to provide various high-voltage pulses required for gas discharge of the PDP, although The parasitic capacitance of the PDP display does not consume energy, but their charging and discharging will result in energy loss in the resistance of the circuit and the resistance of the electrode lead.

The voltage amplitude of the PDP driver circuit is negative tens of volts to several hundred volts, and the operating frequency is 100 to 233 kHz. The design and selection of the driver circuit is especially important for the picture quality and working efficiency of the PDP system.

In the drive circuit of the PDP, the frequency of the address drive circuit is the highest, and therefore, in addition to using the energy recovery technique in the address drive circuit, lowering the pulse voltage of the address drive circuit can also significantly reduce the address power consumption. The following methods can be used to reduce the address voltage pulse.

â— AwD method - that is, "display at the same time". Addressing, sustaining, and erasing pulses are applied together to reduce the addressing voltage, thereby reducing unwanted power consumption. At the same time, since the sustain time occupies most of the time of one subfield, the frequency of sustain pulses can be reduced.

◠Erase addressing method—that is, enter the sustain lighting phase after initialization. After the gray level reaches the requirement, these units are extinguished by erasing addressing. Therefore, the addressing of a single pixel in each field is only once. Moreover, the lower erase voltage and current can be used to effectively reduce the addressing power consumption.

â— Change the working mode of the pulse circuit - even if the switching element works as much as possible when the switching transistor voltage or current is close to zero, it is turned on or off (ZVS or ZCS), which can reduce the switching loss of the device itself.

In large-size PDP displays, row and column driver ICs consume a lot of power. Its power consumption is roughly divided into three parts: logic part, level shift register and high voltage drive part. Under normal circumstances, the logic part consumes less than 20mW, and the level shift register part is below 200mW. The invalid power consumption of the high-voltage drive circuit due to the charge and discharge of the screen capacitor part mainly comes from the parasitic load in the loop-resistance component. Loss. The presence of such a resistance component is unavoidable, but for the electrical energy charged and discharged by the capacitor, the driver IC can try to recover a part by means of a built-in energy recovery circuit.

In order to meet the requirements of high-voltage device performance and reduce the useless power consumption of the high-voltage driver, the PDP driver IC needs to adopt the following stricter control measures than the common integrated circuit in design and process.

â— Adopt SOI process structure, energy loss can be greatly reduced compared with conventional power modules

â— Using dielectric isolation, the output clamp diode inside the driver IC can avoid crosstalk

â— Special treatment for internal component structure and layout, and internal control can eliminate the penetration current during high voltage switching

3 MOS tube selection parameters The appropriate power field effect transistor (MOSFET) enables the drive circuit to operate with high efficiency and stability, and the life is satisfactory. The MOSFET transition is required to be fast enough to reduce switching losses; the on-resistance is small enough to reduce conduction losses; the turn-off resistance is large enough to improve isolation.

Among them, the drain-source on-resistance Rds(on), the reverse recovery time trr, the input capacitance Ciss, and the total gate charge Qg need to be carefully considered. Low on-resistance helps reduce conduction losses, especially for MOSFETs associated with "energy recovery circuits." Low on-resistance helps improve energy recovery efficiency and reduce PDP power dissipation. Trr, Ciss, and Qg affect the switching speed of the MOSFET. Low parameter values ​​can speed up the MOSFET conversion process and help reduce the switching loss of the MOSFET. In addition, the low Ciss and Qg parameters can reduce the drive power of the MOSFET gate and simplify the design of the gate drive circuit.

The gate drive circuit is an external factor that affects the switching loss of the MOS transistor. An excellent gate drive circuit combined with a high-performance MOSFET can produce a high-performance PDP drive circuit.

4 phosphor material

Phosphors for PDP and phosphors for fluorescent lamps are very similar. The phosphors used in PDP are Y2O3:Eu red powder, (Gd,Y)BO3:Eu red powder, Zn2SiO4:Mn and BaAl12O19:Mn green powder, and BaMgAl14O23:Eu and MgBaAl10O17: Eu blue powder. (Gd, Y) BO3:Eu powder and BaAl12O19:Mn powder have a long decay time, and the decay time of Zn2SiO4:Mn is longer for practical applications, so it is necessary to research and develop new luminescent materials. Phosphor materials directly affect the luminous efficiency and overall life of PDP TVs. Usually the life indicator of a plasma TV is the time when the brightness is reduced to half. A new generation of long-life, high-brightness PDP-specific phosphors has been commercialized.

5 Electrode structure is a very effective measure to increase the brightness and luminous efficiency of PDP by increasing the electrode gap. However, if the electrode gap is increased, the required operating voltage will increase. To solve this problem, a floating electrode F can be added between the sustain and scan electrodes (X electrode and Y electrode). The floating electrode does not apply a voltage signal during unit operation, but during a single sustain voltage pulse, a certain induced potential is generated. Since the distance between the F electrode and the X and Y electrodes on both sides thereof is small, it is easy to generate a discharge first at the two gaps. Under their guiding action, a long gap discharge between X and Y is caused, thereby reducing the sustain voltage required for the PDP.

6 Others include the logic control part, the main core board, etc., all need to fully consider the problem of reducing the useless power consumption. For example, the gated clock can be used in the logic control part, and all internal registers can be turned off in the standby state. Eliminate the purpose of useless power consumption.

Based on the above analysis, it can be seen that reducing PDP power consumption can be considered from multiple angles. The correct approach is multi-pronged approach, going hand in hand, from power supply, drive mode, phosphor material, discharge cell structure and new high-voltage process. Start with the goal of maximizing efficiency.

Industry Controller PCBA,Circuit Board Assembly ,Circuit Board Manufacturing ,Printed Board Assembly

LED light Co., Ltd. , http://www.nbpcbassembly.com