According to the PCIe protocol, after the device is started, the PCIe device must meet the requirements of the startup time, that is, within 100 ms after power-on, the initialization of the PCIe device is completed. If the PCIe device startup time requirement cannot be met, lspci may not be able to detect the FPGA-based PCIe device, and a reboot server is required. As we all know, the scale of FPGA chips is getting larger and larger, so what can we do to meet the requirements of the startup time of PCIe devices?

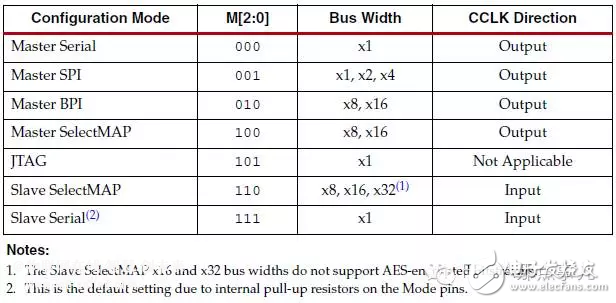

The common configuration modes of 7 series FPGAs are shown in the figure below:

SelectMAP and Master / SlaveSerial are Xilinx's early FPGA two configuration modes. The SPI configuration mode is the SPI interface which allows the FPGA to read the standard industrial SPI Flash as the configuration data storage medium. Similarly, the BPI configuration mode means that the FPGA can be used from an industrial Standard parallel NOR Flash read configuration data. Obviously, for the design of a single FPGA chip, the BPI configuration mode is the fastest way to configure the FPGA. In BPI configuration mode, the configuration clock can select internal CCLK or external EMCCLK. The following formula is the formula to calculate the FPGA configuration time. As can be seen from the formula, for the same type of FPGA, the smaller the bitstream size (see Appendix 1 for the 7 series bitstream size size), the higher the frequency of the configuration clock, the bit width of the data line The larger, the shorter the configuration time.

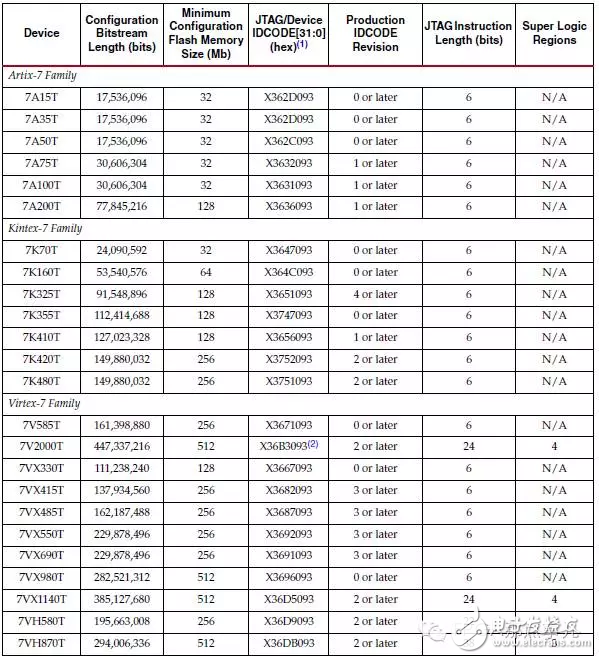

If you use CCLK, the maximum configuration rate is 66Mhz, so in the need to configure FPGA at high speed, external EMCCLK is required to meet the configuration time requirements. The calculation method of the maximum frequency of EMCCLK is shown in the following formula, and cannot exceed the maximum value defined in the DS181, DS182, and DS183 documents. In the 7 series, the common EMCCLK clock frequency is 100Mhz. For example, for the K7325T, by referring to the bitstream size of 91,548,896 bits (87.3Mb), the EMCCLK clock frequency is 100Mhz, and the data bit width is 16, the configuration time is 57ms, which can meet the PCIe device startup time requirements.

After confirming to adopt BPI mode configuration and external configuration clock EMCCLK, what should FPGA design do? First of all, EMCCLK must be introduced into the FPGA, so at the top level of logic, there must be a definition of EMCCLK, as shown below:

Input emcclk;

When generating a bitstream, you need to make pin constraints on EMCCLK as follows:

set_property IOSTANDARD LVCMOS18 [get_ports emcclk]

set_property PACKAGE_PIN R24 [get_ports emcclk]

You also need to add the following constraints in xdc, which can also be done in the graphical interface. Adding in xdc can reduce the interaction of the graphical interface and improve design efficiency.

set_propertyBITSTREAM.CONFIG.EXTMASTERCCLK_EN DIV-1 [current_design]

set_propertyBITSTREAM.CONFIG.BPI_SYNC_MODE TYPE2 [current_design]

If you find that you still cannot meet the 100ms requirement through the calculation of the above formula, you can also try the following methods to solve the problem of configuring the FPGA. The first is relatively simple. When generating a bitstream, you can choose to compress the size of the bitsteam. This setting can be done through the graphical interface, or by adding the Compress parameter in xdc. The second method is more troublesome, you can use Tandem ConfiguraTIon, please refer to xapp1179 for details. Through the calculation of the formula and the selection of the above methods, the design can finally meet the requirements of the PCIe device startup time.

Appendix: 7 series FPGA bitstream size

The latest Windows has multiple versions, including Basic, Home, and Ultimate. Windows has developed from a simple GUI to a typical operating system with its own file format and drivers, and has actually become the most user-friendly operating system. Windows has added the Multiple Desktops feature. This function allows users to use multiple desktop environments under the same operating system, that is, users can switch between different desktop environments according to their needs. It can be said that on the tablet platform, the Windows operating system has a good foundation.

Windows Tablet,New Windows Tablet,Tablet Windows

Jingjiang Gisen Technology Co.,Ltd , https://www.gisentech.com